Convert binary floating-point real numbers into denary and vice versa

Binary Floating-Point Representation (A-Level Computer Science)

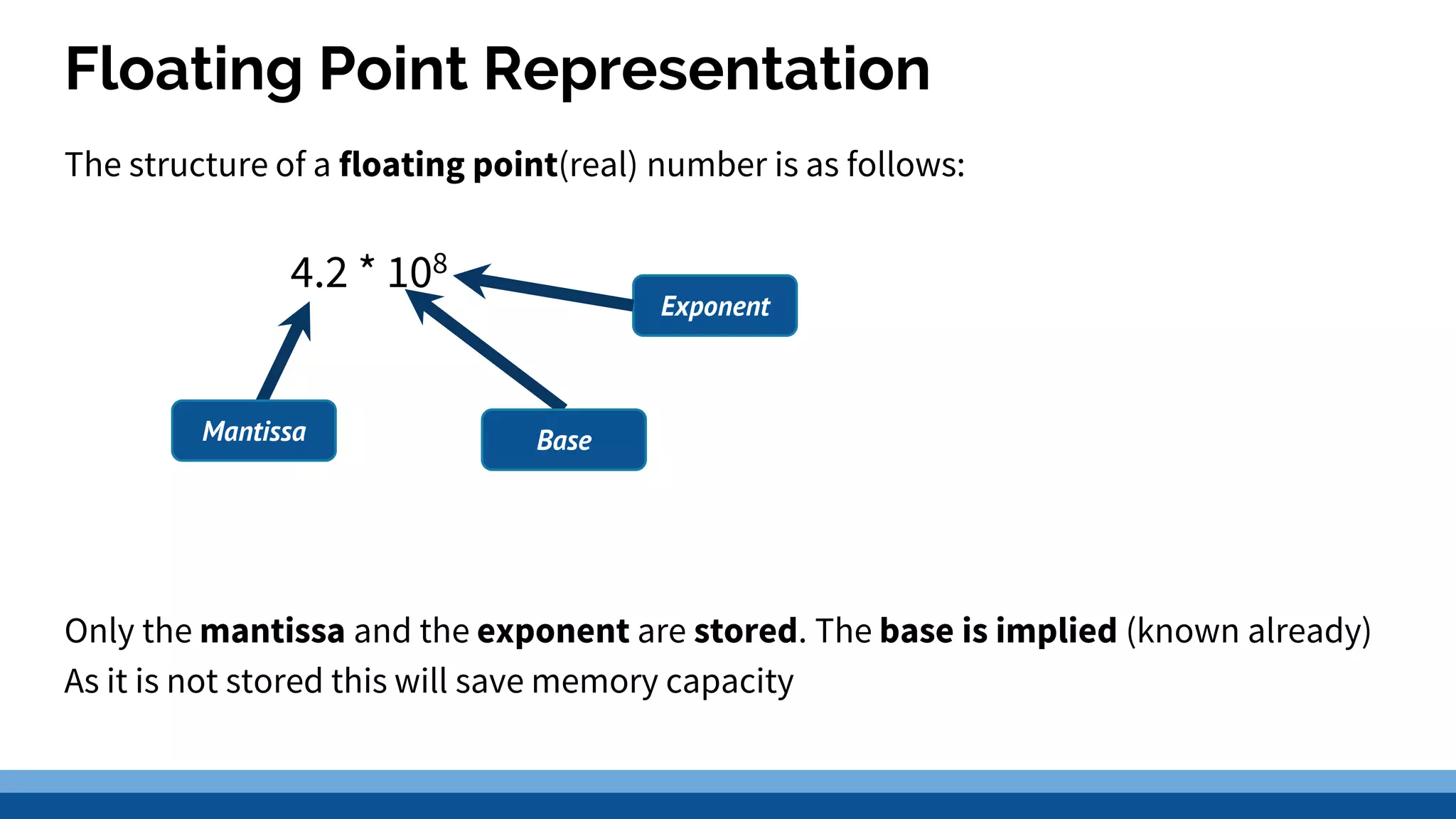

Binary floating-point representation is used to store real numbers that include fractional parts. It works in a similar way to standard form (scientific notation) in denary.

In denary, a number may be written as:

\[ \text{Number} = \text{Mantissa} \times 10^{\text{Exponent}} \]

In binary floating-point, the base is 2 instead of 10:

\[ \text{Number} = \text{Mantissa} \times 2^{\text{Exponent}} \]

The mantissa contains the significant digits, and the exponent shows how far the binary point moves.

Structure of Floating-Point Representation

A floating-point number is stored in two parts:

- Mantissa – signed binary fraction

- Exponent – signed integer showing shift

Both are usually stored using two’s complement.

Normalised Form

A floating-point number is normalised when:

- The first two bits of the mantissa are different

This ensures maximum precision.

Examples:

Valid normalised mantissa:

\[ 0.101101 \]

Invalid (not normalised):

\[ 0.001011 \]

Converting Binary Floating-Point to Denary

Step-by-Step Method

- Convert mantissa to denary fraction

- Convert exponent to denary integer

- Apply formula: \[ \text{Number} = \text{Mantissa} \times 2^{\text{Exponent}} \]

Example 1

Mantissa:

\[ 0.101_2 \]

Exponent:

\[ 010_2 \]

Step 1: Convert mantissa

\[ 0.101_2 = (1 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3}) \]

\[ = 0.5 + 0 + 0.125 \]

\[ = 0.625 \]

Step 2: Convert exponent

\[ 010_2 = 2 \]

Step 3: Apply formula

\[ 0.625 \times 2^2 \]

\[ = 0.625 \times 4 \]

\[ = 2.5 \]

Final Answer: 2.5 denary

Converting Denary to Binary Floating-Point

Step-by-Step Method

- Convert number to binary

- Move binary point to normalised form

- Count places moved

- This gives exponent

- Mantissa is normalised number

Example 2

Convert:\[ 6.5_{10} \]

Step 1: Convert to binary

\[ 6 = 110 \]

\[ 0.5 = 0.1 \]

\[ 6.5 = 110.1 \]

Step 2: Normalise

\[ 0.1101 \times 2^3 \]

Step 3: Result

Mantissa:

\[ 0.1101 \]

Exponent:

\[ 011 \]

Negative Numbers

If the number is negative:

- Mantissa is stored in two’s complement

Exponent remains normal signed integer.

Why Floating-Point is Used

Floating point allows representation of:

- Very large numbers

- Very small numbers

- Fractional numbers

Example:

\[ 0.0000000000000000001 \]

Precision and Limitations

Floating-point numbers have limited precision.

This causes:

- Rounding errors

- Loss of accuracy

Example:

\[ 0.1_{10} \]

Cannot be stored exactly in binary.

Summary

- \[ \text{Number} = \text{Mantissa} \times 2^{\text{Exponent}} \]

- Mantissa stores value

- Exponent stores shift

- Normalisation improves precision

- Two’s complement used for negatives

Exam-Style Questions

1. Convert the following floating-point number to denary:

Mantissa:

\[ 0.101 \]

Exponent:

\[ 011 \]

2. Convert the denary number 9.25 to floating-point form.

3. Explain why normalisation is used.

4. Convert:

\[ 0.01101 \times 2^4 \]

to denary.

Create an account or Login to take a Quiz

Log in to suggest improvements to this note.